Introduction to Counters in Verilog Programming Language

Hello, fellow Verilog enthusiasts! In this blog post, I will introduce you to the concept of Counters in Verilog Programming Language. Counters are essential components that allow you to count events, clock cycles, or pulses in your digital designs. They are typically used in timing circuits, state machines, and frequency dividers, providing a reliable way to track and manage sequences.

Counters can be classified into different types, such as 4-bit Counters, Ripple Counters, and Straight Ring Counters, Johnson Counters, Mod-N Counters and Gray Counters each serving a specific purpose in controlling the flow of data. Let’s take a look at some examples of counters and how they can enhance your digital designs and system functionality.

What are Counters in Verilog Programming Language?

Counters in Verilog are sequential circuits used to count events or sequences, typically driven by clock pulses. They are implemented using flip-flops and are widely used in various applications like event counting, timing control, frequency division, and digital state machines. Counters store a number in binary format, and on each clock cycle, the value is incremented or decremented based on the design.

There are different types of counters, each suited for specific use cases. Below are detailed explanations of some common types of counters, including 4-bit counters, ripple counters, straight ring counters, Johnson counters, Mod-N counters, and Gray counters.

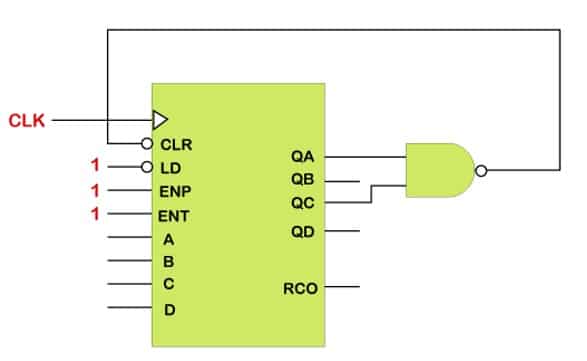

1. 4-bit Counters

A 4-bit counter can count from 0 to 15 (i.e., 2^4 – 1) because it uses 4 flip-flops, each storing a single bit. These counters can be up counters (which count upwards) or down counters (which count downwards). The value changes on every clock cycle and resets after reaching the maximum value (for an up counter) or the minimum value (for a down counter).

2. Ripple Counters (Asynchronous Counters)

A ripple counter, also known as an asynchronous counter, is a counter in which each flip-flop is triggered by the output of the previous flip-flop, rather than all being triggered by the clock signal simultaneously. This causes a slight delay, or “ripple effect,” between the flip-flops toggling, as each flip-flop waits for the previous one to change state.

3. Straight Ring Counters

A straight ring counter (or simply ring counter) is a circular shift register where only one flip-flop holds the logic 1, while all others hold 0. On each clock cycle, the 1 shifts to the next flip-flop. The counter “rings” as the single 1 rotates through the sequence of flip-flops.

4. Johnson Counters (Twisted Ring Counters)

A Johnson counter, also known as a twisted ring counter, is similar to a ring counter, but the inverted output of the last flip-flop is fed back to the input of the first flip-flop. This generates a longer sequence than a simple ring counter and has 2n states for an n-bit Johnson counter.

5. Mod-N Counters (Modulo Counters)

A Mod-N counter is a counter that counts from 0 to N-1 and then resets to 0. For example, a Mod-10 counter (also called a decade counter) counts from 0 to 9 and then resets. This type of counter is widely used in clocks, timers, and event counters where a specific count is needed.

6. Gray Code Counters

A Gray code counter counts in such a way that only one bit changes between consecutive states. This makes it useful in systems that require minimal changes between states to reduce noise or prevent glitches, such as in position encoders.

Why we need Counters in Verilog Programming Language?

Counters are essential in Verilog programming for managing a wide range of operations in digital systems. Here are key reasons why counters are needed in Verilog:

1. Event Counting

Counters are used to count occurrences of specific events, such as pulses, signals, or clock cycles. For example, in digital systems, counters can track how many times a button has been pressed or how many clock cycles have passed.

2. Timing and Delay Management

In digital circuits, precise timing is crucial. Counters are used to implement timers and delays by counting clock cycles. For example, a counter can create a delay by counting a specific number of clock pulses before triggering an action.

3. Frequency Division

Counters are often used to divide the frequency of clock signals. This is critical in applications where a lower frequency clock signal is needed from a high-frequency clock source. For instance, dividing a clock frequency by two or four is a common task that counters handle efficiently.

4. Sequencing Operations

In finite state machines (FSMs) and other control circuits, counters manage the order of operations. They can control the transitions between different states based on the count value, ensuring that tasks are executed in the correct sequence.

5. Address Generation

In memory and data storage applications, counters help generate sequential memory addresses. For example, a counter can be used to increment memory addresses when reading or writing data, ensuring the correct location is accessed at each step.

6. Digital Clocks and Timers

Counters are fundamental components of digital clocks and timers, where they count clock pulses to track time intervals. For example, in a stopwatch or timer, counters are used to track seconds, minutes, or even milliseconds by counting clock cycles.

7. Pulse Width Modulation (PWM) Control

Counters are used in Pulse Width Modulation (PWM) circuits to control the duty cycle. By counting clock cycles, a counter determines how long a signal stays high or low, which is critical for controlling devices like motors or LEDs.

8. Modulus Counting

In applications where you need to count to a specific value and then reset, modulus counters (Mod-N counters) are used. This is useful in systems like frequency dividers or digital clocks, where a counter counts up to a certain number and then resets to start over.

9. Cyclic Redundancy Checks (CRC)

Counters play an essential role in error detection algorithms, such as Cyclic Redundancy Check (CRC), where the system must count and validate data packets. By counting specific bits or packets, counters ensure that the correct amount of data is processed.

10. Synchronization and Control Signals

In multi-clock domain systems or systems with complex timing requirements, counters help synchronize and generate control signals. For example, they can generate enable or disable signals after counting a predefined number of clock pulses.

11. State Tracking

Counters are essential in tracking and managing system states in state machines. They provide a structured way to move through different stages of a process, ensuring that the correct sequence of events occurs in digital systems.

Example of Counters in Verilog Programming Language

Here are examples of different types of counters in Verilog, which demonstrate how counters are implemented and used in Verilog Programming Language:

1. 4-bit Up Counter

A 4-bit counter counts from 0 to 15 and then wraps around to 0. This is a simple up-counter that increments on each clock cycle.

Verilog Code:

module up_counter_4bit (

input clk, // Clock signal

input reset, // Reset signal

output reg [3:0] count // 4-bit counter output

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0000; // Reset the counter to 0

else

count <= count + 1; // Increment the counter on each clock cycle

end

endmoduleExplanation:

- clk: Controls the clock pulses that increment the counter.

- reset: Resets the counter to zero.

- count: Holds the current 4-bit value and increments on each clock pulse.

- The counter counts from

0000(0) to1111(15) and wraps around to0000.

2. Ripple Counter (Asynchronous Counter)

A ripple counter triggers each flip-flop in sequence based on the output of the previous flip-flop. This creates a ripple effect as the count propagates through the flip-flops.

Verilog Code:

module ripple_counter (

input clk, // Clock signal

input reset, // Reset signal

output [3:0] count // 4-bit counter output

);

reg [3:0] q;

always @(posedge clk or posedge reset) begin

if (reset)

q <= 4'b0000; // Reset the counter to 0

else

q <= q + 1; // Increment the counter

end

assign count = q; // Output the counter value

endmoduleExplanation:

- Ripple effect: Each flip-flop toggles based on the previous flip-flop’s output.

- Asynchronous design: Not all flip-flops are triggered by the clock signal, leading to slight propagation delays.

- The counter counts upwards with each clock pulse, introducing delays as the count ripples through the flip-flops.

3. Straight Ring Counter

A straight ring counter uses a shift register where only one flip-flop holds a 1, and it shifts this 1 through the register on each clock pulse.

Verilog Code:

module ring_counter (

input clk, // Clock signal

input reset, // Reset signal

output reg [3:0] count // 4-bit output

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0001; // Set the initial state to 0001

else

count <= {count[2:0], count[3]}; // Shift left and wrap the MSB

end

endmoduleExplanation:

- clk: Shifts the value with every clock pulse.

- reset: Resets the counter to

0001, the initial state. - Ring behavior: Only one

1exists at a time, and it circulates through the register in a ring pattern.

4. Johnson Counter (Twisted Ring Counter)

A Johnson counter, or twisted ring counter, is a shift register with feedback. It generates a longer sequence of 2n states for an n-bit counter by feeding back the inverted output of the last flip-flop.

Verilog Code:

module johnson_counter (

input clk, // Clock signal

input reset, // Reset signal

output reg [3:0] count // 4-bit output

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0000; // Reset to 0000

else

count <= {count[2:0], ~count[3]}; // Shift and invert MSB

end

endmoduleExplanation:

- clk: Controls the shift on each clock cycle.

- reset: Initializes the counter to

0000. - Inversion feedback: The counter shifts left, and the inverted MSB is fed back into the LSB.

- 2n states: A 4-bit Johnson counter cycles through 8 unique states.

5. Mod-N Counter (Modulus Counter)

A Mod-N counter counts from 0 to N-1 and resets back to 0. Here’s an example of a Mod-10 counter (decade counter) that counts from 0 to 9 and then resets.

Verilog Code:

module mod_10_counter (

input clk, // Clock signal

input reset, // Reset signal

output reg [3:0] count // 4-bit output

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0000; // Reset to 0

else if (count == 4'b1001) // If count is 9

count <= 4'b0000; // Reset to 0

else

count <= count + 1; // Increment the counter

end

endmoduleExplanation:

- clk: Drives the count upwards.

- reset: Resets the counter to 0.

- Mod-10 behavior: The counter counts from

0000(0) to1001(9) and then wraps around to0000.

6. Gray Code Counter

A Gray code counter ensures that only one bit changes between consecutive states. This is useful in situations where you want to minimize state transition errors, such as in position encoders.

Verilog Code:

module gray_code_counter (

input clk, // Clock signal

input reset, // Reset signal

output reg [3:0] count // 4-bit Gray code output

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0000; // Reset to 0

else

count <= count ^ (count >> 1); // Convert binary to Gray code

end

endmoduleExplanation:

- clk: Updates the counter value on each positive edge.

- Gray code conversion: The binary value is XORed with itself, shifted right by 1, to generate Gray code.

- Single-bit changes: Only one bit changes between consecutive Gray code values.

Advantages of Counters in Verilog Programming Language

Counters are integral components in digital systems, and using them in Verilog offers many benefits, including versatility, efficiency, and ease of implementation. Below are the key advantages of using counters in Verilog programming:

1. Simplified Design and Implementation

Ease of Coding: Verilog simplifies the process of designing counters, enabling designers to create complex counters with just a few lines of code. Counters like up, down, and modulus counters are easily implemented using procedural blocks like always and edge-triggered logic.

Modular Design: Counters can be reused as modules in larger systems, allowing for easy integration into complex digital designs.

2. Efficient Timing and Synchronization

Accurate Time Control: Counters help in generating precise time intervals by counting clock cycles, making them essential in applications like timers, clocks, and synchronization in digital circuits.

Clock Frequency Division: Counters can be used to divide clock frequencies, creating lower-frequency signals from higher-frequency sources. This is useful in applications where multiple devices with different clock speeds need to operate in sync.

3. Versatility and Flexibility

Different Types of Counters: Verilog allows the implementation of various types of counters like up counters, down counters, up/down counters, modulus counters, ripple counters, ring counters, Gray code counters, and more. This flexibility makes them suitable for a wide range of applications.

Mod-N Counters: Counters can be tailored to count up to a specific value (Mod-N) and then reset, which is useful for applications like digital clocks, event counters, and state machines.

4. Low Hardware Complexity

Minimal Resources: Counters are implemented with simple flip-flops and combinational logic, which results in minimal hardware resource consumption. This makes them ideal for use in systems with limited resources.

Power Efficiency: Counters can be designed to consume low power, especially asynchronous counters like ripple counters, which only trigger one flip-flop at a time.

5. Data Flow Control and Sequencing

State Control: Counters play a key role in finite state machines (FSMs), helping to control the transitions between different states in an orderly manner. This ensures correct sequencing of operations in digital systems.

Data Transfer: In digital communication protocols, counters help control data flow, for instance, by tracking the number of bits transmitted or received.

6. Error Detection and Correction

Gray Code Counters: Gray code counters are particularly useful for minimizing errors in state transitions, as only one bit changes between consecutive states. This reduces the chances of glitches and is valuable in applications like digital encoders.

Cyclic Redundancy Checks (CRC): Counters are used to count bits and help in error detection algorithms like CRC, ensuring reliable data transmission.

7. Precise Event Counting

Event Monitoring: Counters are essential for tracking the number of events, pulses, or occurrences in systems such as real-time clocks, frequency meters, or other monitoring devices. Verilog allows you to implement event counters efficiently in hardware.

Interrupt Generation: Counters can generate interrupts after counting a specific number of events, enabling automatic responses from the system without continuous manual intervention.

8. Simulation and Debugging

Simulation Friendly: Verilog’s built-in support for counters allows for easier simulation and debugging of digital circuits. By observing counter values in simulation tools, engineers can monitor performance and verify system timing.

Testbench Integration: Counters can be easily integrated into testbenches in Verilog, allowing you to simulate and test complex timing scenarios and operational sequences.

9. Compact Design in FPGA/ASICs

Resource Optimization: Counters are implemented efficiently on FPGAs and ASICs, occupying minimal hardware resources. FPGA-based designs can leverage built-in support for counters in logic blocks, saving both area and power.

Scalability: Verilog allows for scalable counter designs, meaning you can increase the bit-width of a counter without drastically increasing hardware complexity.

10. Real-time Applications

Real-time Processing: Counters are essential in real-time systems where timing, event tracking, and synchronization are critical. Counters ensure that operations are executed at precise intervals, which is crucial for applications like digital signal processing (DSP) and embedded systems.

Disadvantages of Counters in Verilog Programming Language

While counters are highly useful in digital design and are widely used in Verilog programming, there are some limitations and disadvantages associated with them. Here are the key drawbacks:

1. Propagation Delay in Asynchronous (Ripple) Counters

Ripple Effect Delays: In ripple counters (asynchronous counters), each flip-flop triggers the next, causing a ripple effect. This creates propagation delays because the output of one flip-flop must stabilize before the next can change. These delays accumulate and can cause timing issues, especially in high-speed applications.

Lower Speed: The propagation delay limits the speed at which ripple counters can operate, making them unsuitable for high-frequency applications.

2. Limited Scalability

Increased Hardware Resources for Larger Counters: As the number of bits in a counter increases, the number of flip-flops required also increases. This results in higher hardware complexity and resource consumption, which can be a concern in large-scale designs, especially in FPGAs or ASICs with limited resources.

Power Consumption: Larger counters can consume more power due to the increased number of flip-flops and transitions, making them less ideal for power-sensitive applications.

3. Synchronization Issues in Asynchronous Counters

Difficulty in Multiclock Designs: In systems where multiple clocks are involved, asynchronous counters may introduce synchronization problems, leading to glitches or metastability in the design. Synchronizing these counters with other parts of the system can be complex.

Glitches: Asynchronous counters are prone to glitches during state transitions, where multiple flip-flops are switching states at slightly different times, which can cause unpredictable behavior.

4. Limited Flexibility in Specific Applications

Fixed Functionality: Basic counters, such as up or down counters, are designed to perform simple counting operations. They may lack the flexibility needed for more complex designs, such as nonlinear sequences, which require additional control logic or state machines.

Finite Modulus: Mod-N counters count up to a specific value and then reset, which may not be suitable for applications requiring more dynamic or programmable counting ranges.

5. Increased Complexity in Synchronous Counters

Design Complexity: While synchronous counters address the timing issues of ripple counters, they come with increased design complexity. Every flip-flop in a synchronous counter must be triggered by the same clock signal, requiring additional logic to ensure proper operation, especially for counters with more bits.

Longer Setup and Hold Times: Synchronous counters can suffer from setup and hold time violations if not carefully designed, particularly in high-speed circuits where the clock cycle is short.

6. Clock Skew in Large Counters

Distribution of Clock Challenges: In large designs, distributing the clock signal evenly across all flip-flops in a counter can be challenging. Clock skew the difference in arrival times of the clock signal at different flip-flops—can lead to incorrect counting or misalignment of signals.

Increased Clock Load: Synchronous counters introduce more load on the clock signal because every flip-flop is directly connected to the clock, which may require clock buffers or additional clock management circuitry.

7. Power and Area Consumption in Complex Counters

Power Consumption in High-Speed Counters: High-speed counters consume more power, especially when many flip-flops are toggling frequently. This becomes a critical issue in power-sensitive applications, such as battery-powered devices or low-power embedded systems.

Increased Silicon Area: For ASIC designs, counters with a large number of bits or complex features (such as programmable counters) can occupy significant silicon area, increasing the cost of the design.

8. Limited Error Detection and Correction

Potential for Malfunction: Basic counters do not have built-in error detection or correction capabilities. If there is a malfunction in one of the flip-flops (e.g., a stuck bit), the counter may fail to count correctly, leading to incorrect behavior without immediate detection.

Lack of Fault Tolerance: Counters generally lack fault tolerance, making them more vulnerable to errors caused by environmental factors like radiation or electrical noise.

9. Debugging and Verification Challenges

Difficult to Debug Complex Counters: When counters are used as part of complex systems, debugging and verifying the behavior of counters can be challenging. In large designs, it can be difficult to trace issues related to timing, glitches, or synchronization problems.

Simulation Timing Issues: Verilog simulation of counters may not always reflect real-world timing, especially in asynchronous designs, leading to discrepancies between simulation results and actual hardware behavior.

10. Glitches and Spikes in Digital Communication

Hazards and Spikes in Output: In certain designs, counters can introduce glitches (brief unintended pulses) in the output when state transitions occur, particularly in asynchronous designs. These glitches can propagate through the system, leading to unexpected behavior or communication errors in digital protocols.

Discover more from PiEmbSysTech - Embedded Systems & VLSI Lab

Subscribe to get the latest posts sent to your email.