Mastering in Joint Test Action Group (JTAG) Protocol

Hello, fellow engineers and enthusiasts! Today I’m going to share with you some tips and tricks on how to master the Joint Test Action Group (JTAG) protocol, which is a powerful tool for debugging and testing embedded systems. JTAG is a standard that defines how to communicate with devices that have boundary-scan capabilities, such as microcontrollers, FPGAs, CPLDs, and ASICs. JTAG allows you to access the internal registers, memory, and pins of these devices, as well as program them with new firmware. JTAG can also be used to chain multiple devices together and control them from a single interface.

Introduction to JTAG Protocol

The Joint Test Action Group (JTAG) protocol, officially known as IEEE 1149.1, is a vital technology in the world of electronics and digital design. It is a standardized method for testing and debugging integrated circuits (ICs) and printed circuit boards (PCBs). JTAG allows engineers and technicians to gain access to various components within a complex system for testing, programming, and debugging purposes. In this article, we will explore the fundamentals of JTAG, its key features, and how mastering this protocol can significantly benefit professionals in the electronics industry.

History and Inventions of JTAG Protocol

The history of the Joint Test Action Group (JTAG) protocol traces back to the 1980s when it was developed as a solution to the growing challenges in testing and debugging complex digital systems, particularly integrated circuits (ICs) and printed circuit boards (PCBs). Let’s delve into the key milestones that shaped the history of JTAG:

- Formation of the Joint Test Action Group (JTAG): In 1985, a group of representatives from leading companies in the electronics industry, including Texas Instruments, IBM, Intel, and Hewlett-Packard, formed the Joint Test Action Group. The primary goal of this group was to create a standardized method for testing and debugging electronic systems that were becoming increasingly complex and difficult to test using traditional methods.

- Early Developments and Contributions: Among the key contributors to the early development of the JTAG protocol were individuals like Ken Parker from Texas Instruments, who proposed the concept of using a single standardized interface to access multiple pins of an IC or PCB for testing purposes. David Brownell from IBM made significant contributions to the design of the JTAG state machine, which plays a crucial role in controlling testing operations and transitions.

- Introduction of the JTAG Standard (IEEE 1149.1): In 1987, the Joint Test Action Group officially released the JTAG standard, known as IEEE 1149.1. This standard was titled “Standard Test Access Port and Boundary-Scan Architecture” and provided a comprehensive framework for implementing the JTAG protocol in electronic devices. The JTAG standard defined the necessary signals and their functions, the state machine operations, and boundary scan testing techniques.

- Rapid Adoption and Industry Impact: The JTAG protocol quickly gained acceptance in the electronics industry due to its numerous advantages. By offering a standardized approach to testing, JTAG greatly simplified the testing process for complex systems. It allowed engineers to perform non-intrusive testing and debugging, even in cases where physical access to individual pins was difficult or impossible. As a result, JTAG became an integral part of the design, manufacturing, and testing processes for a wide range of electronic products.

- Evolution and Extensions: As technology continued to advance, the JTAG standard evolved to meet the changing needs of the industry. Additional standards and extensions were introduced to enhance the capabilities of JTAG. For example, IEEE 1149.4 addressed analog testing features, and IEEE 1149.6 focused on testing challenges in high-speed digital systems.

- Integration into Industry Standards: JTAG has been integrated into various other industry standards to further expand its application and benefits. Notably, it became a part of IEEE 1500, which focuses on testing intellectual property (IP) cores within integrated circuits.

Inventions of the JTAG Protocol

The invention of JTAG can be attributed to a collaborative effort by several individuals who were part of the Joint Test Action Group. The JTAG group, formed in 1985, consisted of representatives from various companies in the electronics industry, including Texas Instruments, IBM, Intel, Hewlett-Packard, and others. Their main goal was to create a standardized approach for testing and debugging complex ICs and PCBs.

The key inventors and contributors to the JTAG protocol include:

- Ken Parker (Texas Instruments): Ken Parker is often considered the primary inventor of JTAG. He proposed a technique for using a single, standardized interface to access multiple pins of an IC or PCB for testing purposes. His contributions laid the foundation for the JTAG protocol.

- David Brownell (IBM): David Brownell played a crucial role in the development of the JTAG state machine, which is an essential part of the protocol. The state machine allows for controlling the operations and transitions during the testing process.

- Terry Burcham (Hewlett-Packard): Terry Burcham made significant contributions to defining the architecture and specifications of the JTAG protocol.

Standardization of the JTAG Protocol

In 1987, the Joint Test Action Group officially released the JTAG standard as IEEE 1149.1, which is also known as the Standard Test Access Port and Boundary-Scan Architecture. This standard provided a comprehensive framework for implementing the JTAG protocol in electronic devices.

The JTAG standard was quickly adopted by the electronics industry due to its numerous advantages, including reduced test time, non-intrusive testing, and in-system programming capabilities. As a result, JTAG became an integral part of the design, manufacturing, and testing processes for a wide range of electronic products.

Evolution and Extensions of the JTAG Protocol

Over time, the JTAG standard continued to evolve to meet the changing needs of the industry. Additional standards and extensions were introduced to enhance the capabilities of JTAG. Some notable extensions include IEEE 1149.4, which provides analog testing features, and IEEE 1149.6, which addresses testing challenges in high-speed digital systems.

JTAG has also been integrated into other industry standards, such as IEEE 1500, which focuses on testing intellectual property (IP) cores within integrated circuits.

Architecture of the JTAG Protocol

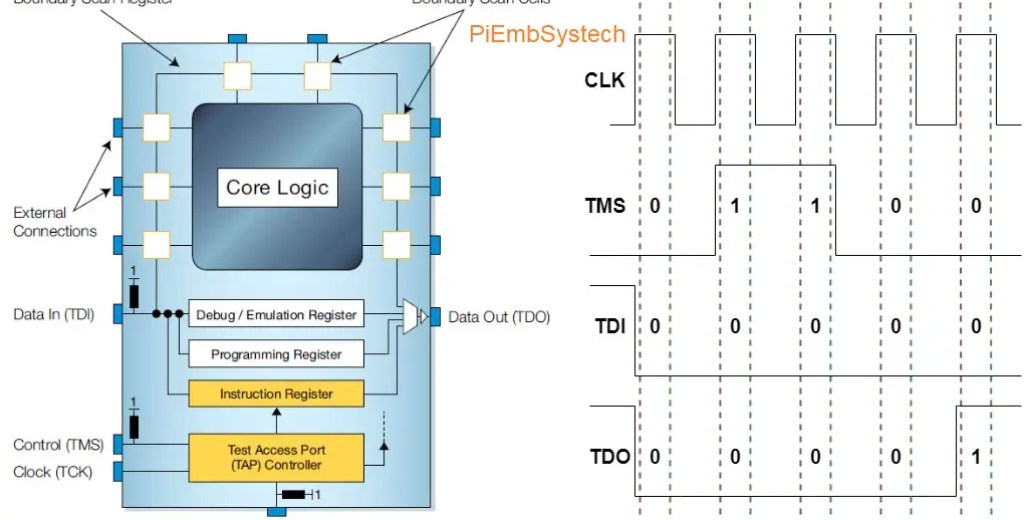

The IEEE-1149.1 JTAG standard outlines the behavior of IC scan logic to ensure seamless interaction between components, systems, and test tools. Integrated circuits (ICs) incorporate logic cells, known as boundary-scan cells, situated between the system logic and the signal pins or balls that establish connections to the printed circuit board (PCB). These cells offer distinct test capabilities—some function as input, others as output, and some possess bidirectional functionalities.

The architecture of the Joint Test Action Group (JTAG) protocol, also known as IEEE 1149.1, is designed to provide a standardized method for testing and debugging integrated circuits (ICs) and printed circuit boards (PCBs). The JTAG architecture consists of several key components that work together to enable efficient and non-intrusive testing of complex digital systems.

Let’s explore the major elements of the JTAG architecture:

- Test Access Port (TAP): At the core of the JTAG architecture is the Test Access Port (TAP). The TAP is a digital state machine that controls the access to the internal components of the device under test (DUT). It manages the flow of data and control signals between the external testing equipment and the internal circuitry of the DUT.

The Test Access Port consists of four mandatory signals and an optional fifth signal:

- Test Clock (TCK): A clock signal that synchronizes data transfer between the test equipment and the DUT.

- Test Mode Select (TMS): A control signal that determines the state transitions of the TAP’s state machine.

- Test Data Input (TDI): A bidirectional data signal used to input test data into the DUT.

- Test Data Output (TDO): A bidirectional data signal used to output test data from the DUT.

- Test Reset (TRST) (optional): An optional signal used for resetting the TAP.

- JTAG State Machine: The Test Access Port incorporates a state machine that governs the operation of the JTAG protocol. The state machine defines the different states that the TAP can be in and the transitions between these states. Each state corresponds to a specific operation, allowing the TAP to perform various functions during testing and debugging.

The primary states of the JTAG state machine are as follows:

- Test-Logic-Reset (TLR): The initial state after power-up or a test reset, where the TAP is held in a stable state.

- Run-Test/Idle (RTI): The TAP is in an idle state waiting for instructions or test data.

- Select-DR-Scan (SDR): The state where the TAP is prepared to shift data into or out of the Data Register (DR) of the DUT.

- Capture-DR (CDR): The state where the input data to be shifted into the DR is captured.

- Shift-DR (SDR): The state where the data is shifted into or out of the DR.

- Exit1-DR (EDR1): The state where the TAP leaves the Shift-DR state and prepares for the next operation.

- Exit2-DR (EDR2): The state where the TAP exits the Shift-DR state after the last bit has been shifted.

- Boundary Scan Registers: One of the essential features of the JTAG architecture is the Boundary Scan Register. This register allows for the testing of the interconnections (nets) between different ICs on a PCB. It consists of input (Bypass) and output (Capture, Shift, and Update) cells for each pin of the DUT. Boundary scan testing helps detect faults related to open circuits, short circuits, and other connectivity issues.

- Instruction Register (IR) and Data Register (DR): The Instruction Register (IR) and Data Register (DR) are part of the JTAG architecture and facilitate communication and control with the internal components of the DUT. The IR is used to select and control various operations, such as reading and writing data to and from internal registers. The DR is used for data shifting during testing and programming.

JTAG Protocol Instructions

IEEE-1149.1 mandates specific instructions that must be adhered to for full JTAG compliance. To achieve JTAG compliance, devices are required to incorporate and implement these instructions.

- EXTEST: The EXTEST instruction serves the purpose of conducting interconnect testing. When activated, it connects the mandatory boundary-scan register between TDI and TDO, effectively placing the device in an “external” test mode. In this mode, boundary-scan output cells drive test data onto the device pins, while input cells capture data from those pins. This instruction is pivotal for boundary-scan testing.

- SAMPLE/PRELOAD: The SAMPLE/PRELOAD instruction shares similarities with EXTEST but enables the boundary-scan device to stay in mission/functional mode while still linking the boundary-scan register to TDI and TDO. When using the SAMPLE/PRELOAD instruction, the boundary-scan register can be accessed through data scans while the device remains operational. This capability is advantageous for preloading data into the boundary-scan register without interrupting the device’s functional behavior, preparing it for subsequent execution of the EXTEST instruction.

- BYPASS: The BYPASS instruction establishes a direct connection between TDI and TDO through a single-bit register, bypassing the longer boundary-scan register of the device—hence its name. BYPASS proves highly advantageous for shortening the boundary-scan chain by excluding devices not required for the current operation. Devices receiving the BYPASS instruction maintain their mission/functional mode while allowing seamless serial data flow to the subsequent device in the chain.

JTAG Protocol TAP Controller

As per the IEEE-1149.1 standard, the TAP controller operates as a 16-state finite state machine, guided by the test clock (TCK) and test mode select (TMS) signals. State transitions are governed by the state of TMS at the rising edge of TCK.

The state machine comprises two analogous paths, facilitating the capture and/or update of data through scanning either the instruction register (IR) or a data register (DR). Figure 2 illustrates the JTAG state machine.

The TAP controller, functioning as a state machine guided by the TMS signal, governs the behavior of the JTAG system. The state-transition diagram depicting this process is presented in this Figure.

Each state within the JTAG state machine has dual exits, enabling control of all transitions through the single TMS signal sampled on TCK. The two primary paths facilitate the setting or retrieval of information from either a data register or the instruction register of the device. The specific data register accessed (e.g. BSR, IDCODES, BYPASS) depends on the value loaded into the instruction register.

JTAG Interface Connectors and their Pinout

JTAG connectors, also known as JTAG headers or JTAG ports, are physical connectors used to establish a connection between a device or printed circuit board (PCB) and the Joint Test Action Group (JTAG) interface. These connectors facilitate the testing, debugging, and programming of the device using the JTAG protocol. There are several different types of JTAG connectors based on their form factor, pin count, and application. Below are some common JTAG connector types:

- 20-Pin JTAG Connector.

- 16-Pin OCDS JTAG Connector.

- 14-Pin JTAG Connector.

- 10-Pin JTAG Connector (ARM JTAG Connector).

- Custom JTAG Connectors.

- Surface Mount JTAG Connectors.

- Flying Lead JTAG Connectors.

1. 20-Pin JTAG Connector:

The 20-pin JTAG connector is one of the most widely used JTAG connectors. It features 20 pins arranged in two rows of ten. This connector type is commonly used in traditional JTAG applications and can be found on many development boards and evaluation platforms. It offers a standard interface for JTAG communication and is compatible with most JTAG programmers and debuggers.

| Pin Number | Signal Name | Pin Description |

|---|---|---|

| 1 | VREF | Reference voltage for the JTAG signals. |

| 2 | TRSTn | Optional Test Reset signal. When pulled low, it resets the JTAG state machine. |

| 3 | TDO | Test Data Output. Data output from the device during testing or debugging. |

| 4 | TCK | Test Clock. Provides the clock signal for shifting data in and out of the device. |

| 5 | GND | Ground reference. |

| 6 | TDI | Test Data Input. Data input to the device during testing or programming. |

| 7 | GND | Ground reference. |

| 8 | TMS | Test Mode Select. Controls the state transitions of the JTAG state machine. |

| 9 | GND | Ground reference. |

| 10 | n/c | Not connected or reserved. |

| 11 | n/c | Not connected or reserved. |

| 12 | n/c | Not connected or reserved. |

| 13 | n/c | Not connected or reserved. |

| 14 | GND | Ground reference. |

| 15 | n/c | Not connected or reserved. |

| 16 | n/c | Not connected or reserved. |

| 17 | n/c | Not connected or reserved. |

| 18 | n/c | Not connected or reserved. |

| 19 | VCC | Power supply voltage for the JTAG interface. |

| 20 | n/c | Not connected or reserved. |

2. 16-Pin OCDS JTAG Connector:

A 16-pin OCDS JTAG (On-Chip Debugging Solution) connector is a type of interface connector used for debugging and programming microcontrollers and other integrated circuits on printed circuit boards (PCBs). JTAG is a standard for debugging and testing electronic devices during development, production, and even in-field operation.

| Pin Number | Signal Name | Pin Description |

|---|---|---|

| 1 | TMS | IEEE 1149.1 |

| 2 | Vdd | I/O ring voltage of CPU |

| 3 | TDO | IEEE 1149.1 |

| 4 | GND | |

| 5 | CPU_CLOCK | Optional |

| 6 | GND | |

| 7 | TDI | IEEE 1149.1 |

| 8 | RESET | Open drain, TriCore: PORST (Power On Reset) |

| 9 | TRST | IEEE 1149.1 |

| 10 | BRKOUT | |

| 11 | TCK | IEEE 1149.1 |

| 12 | GND | |

| 13 | BRKIN | Break Input & OCDS configuration |

| 14 | OCDSE1 | TriCore, OCDS configuration |

| 15 | RCAP1 | Reserved for customer application purposes |

| 16 | RCAP2 | Reserved for customer application purposes |

3. 14-Pin JTAG Connector:

The 14-pin JTAG connector is a reduced pin-count version of the 20-pin connector. It is often used in applications where space is limited, or the device has fewer JTAG-related functionalities. The 14-pin connector provides the essential JTAG signals required for testing and debugging and is commonly found in small form factor devices. The pinout for the 14-pin JTAG connector is as follows:

| Pin Number | Signal Name | Pin Description |

|---|---|---|

| 1 | TRSTn | Optional Test Reset signal. When pulled low, it resets the JTAG state machine. |

| 2 | TDO | Test Data Output. Data output from the device during testing or debugging. |

| 3 | TCK | Test Clock. Provides the clock signal for shifting data in and out of the device. |

| 4 | GND | Ground reference. |

| 5 | TDI | Test Data Input. Data input to the device during testing or programming. |

| 6 | TMS | Test Mode Select. Controls the state transitions of the JTAG state machine. |

| 7 | n/c | Not connected or reserved. |

| 8 | n/c | Not connected or reserved. |

| 9 | n/c | Not connected or reserved. |

| 10 | n/c | Not connected or reserved. |

| 11 | n/c | Not connected or reserved. |

| 12 | GND | Ground reference. |

| 13 | n/c | Not connected or reserved. |

| 14 | n/c | Not connected or reserved. |

4. 10-Pin JTAG Connector (ARM JTAG Connector):

The 10-pin JTAG connector, also known as the ARM JTAG connector, is commonly used in applications involving ARM microcontrollers and processors. ARM-based devices often have a dedicated JTAG port with a 10-pin header. This connector type is designed to provide the necessary JTAG signals for ARM devices and is widely used in embedded systems development.

| Pin Number | Signal Name | Pin Description |

|---|---|---|

| 1 | VTref | Target reference voltage. This pin is used to supply the reference voltage for the JTAG interface on the target board. It’s typically connected to the board’s supply voltage (VCC) or an external reference voltage. |

| 2 | nTRST | Test Reset (active-low). It is an optional pin used to reset the target device, typically for testing purposes. Some devices might not have this pin connected or use it for other purposes. |

| 3 | TDI | Test Data In. This is the data input pin for shifting data into the target’s JTAG TAP (Test Access Port) controller during programming or debugging operations. |

| 4 | TMS | Test Mode Select. This pin is used to control the state transitions of the JTAG TAP controller. It determines whether the JTAG controller is in test mode or in normal operation mode. |

| 5 | TCK | Test Clock. This pin is used to provide the clock signal for synchronizing data transfers between the JTAG host and the target device. |

| 6 | GND | Ground. This pin is connected to the ground reference of the target system and provides the return path for all the JTAG signals. |

| 7 | GND | Ground. Another ground pin to ensure proper grounding and reduce noise in the JTAG interface. |

| 8 | TDO | Test Data Out. This is the data output pin for shifting data out from the target’s JTAG TAP controller during programming or debugging operations. |

| 9 | nRESET | Target Device Reset (active-low). This is an optional pin used to reset the target device. It’s different from nTRST, as it is the device’s main reset, while nTRST is for JTAG-specific reset. |

| 10 | nRESET | Target Device Reset (active-low). Another optional pin used for target device reset. Some devices might have multiple reset pins, providing flexibility based on the specific application. |

It’s essential to note that the ARM JTAG connector might be used in different configurations depending on the specific implementation and target device. For some devices, certain pins like nTRST or the additional nRESET might not be used or have different functions. Always refer to the target device’s datasheet or the development board’s documentation for the correct pinout and usage information.

5. Custom JTAG Connectors:

In some cases, especially in proprietary or specialized applications, custom JTAG connectors may be used. These connectors are tailored to the specific requirements of the device or application and may have a non-standard pin configuration. Custom JTAG connectors are typically found in devices with limited space or unique form factors.

6. Surface Mount JTAG Connectors:

Surface mount JTAG connectors are designed to be mounted directly on the surface of a PCB, providing a low-profile and space-saving solution. They are commonly used in applications where board space is a critical consideration or when the connectors need to be mounted on the bottom side of the PCB.

7. Flying Lead JTAG Connectors:

Flying lead JTAG connectors feature wires or cables attached to the connector, providing flexibility and ease of use. These connectors are often used in testing and debugging scenarios where a fixed connector is not suitable due to device location or orientation.

Working Principle of JTAG Protocol

The JTAG protocol works by providing a standardized method for testing and debugging integrated circuits (ICs) and printed circuit boards (PCBs). It allows engineers to access and control the internal components of a device using a Test Access Port (TAP) and a set of defined states in a state machine. Below is a brief explanation of how JTAG works for debugging from a PC and running code with breakpoints:

- Test Access Port (TAP): The JTAG TAP is a digital state machine that controls access to the internal components of the device under test (DUT). It consists of four or five pins: Test Clock (TCK), Test Mode Select (TMS), Test Data Input (TDI), Test Data Output (TDO), and optionally, Test Reset (TRST). These pins form a communication interface between the external test equipment (usually a PC) and the internal circuitry of the DUT.

- JTAG State Machine: The TAP contains a state machine that governs the operation of the JTAG protocol. The state machine defines various states and the transitions between them. The primary states include Test-Logic-Reset (TLR), Run-Test/Idle (RTI), Select-DR-Scan (SDR), Capture-DR (CDR), Shift-DR (SDR), Exit1-DR (EDR1), and Exit2-DR (EDR2).

- Debugging from a PC: To debug a device using JTAG from a PC, you need a hardware interface that connects the PC to the JTAG interface of the target device. This hardware interface is typically a JTAG adapter or programmer. The PC communicates with the JTAG interface using specialized debugging software, such as Integrated Development Environments (IDEs) or dedicated JTAG debuggers.

The debugging process involves the following steps:

- Connect the JTAG hardware interface to the JTAG interface of the target device.

- Establish communication between the PC and the JTAG interface using the TCK, TMS, TDI, and TDO pins.

- Put the TAP in the desired state, such as Select-DR-Scan (SDR), to access and manipulate internal registers of the device.

- Load the appropriate debugging software on the PC and connect to the target device via the JTAG interface.

- The debugging software allows you to read and write data to internal registers, set breakpoints, halt the processor, and perform other debugging operations.

- Running Code with Breakpoints: Once the PC is connected to the target device through the JTAG interface, you can load your code onto the device’s memory using JTAG. After loading the code, you can execute it just like any other program.

For using breakpoints, the debugging software communicates with the processor through the JTAG interface and instructs it to stop execution at specific memory addresses (breakpoints). When the processor reaches a breakpoint, it halts its operation, allowing you to inspect the program state, memory contents, and register values. This enables you to analyze the program’s behavior and find bugs or errors in the code.

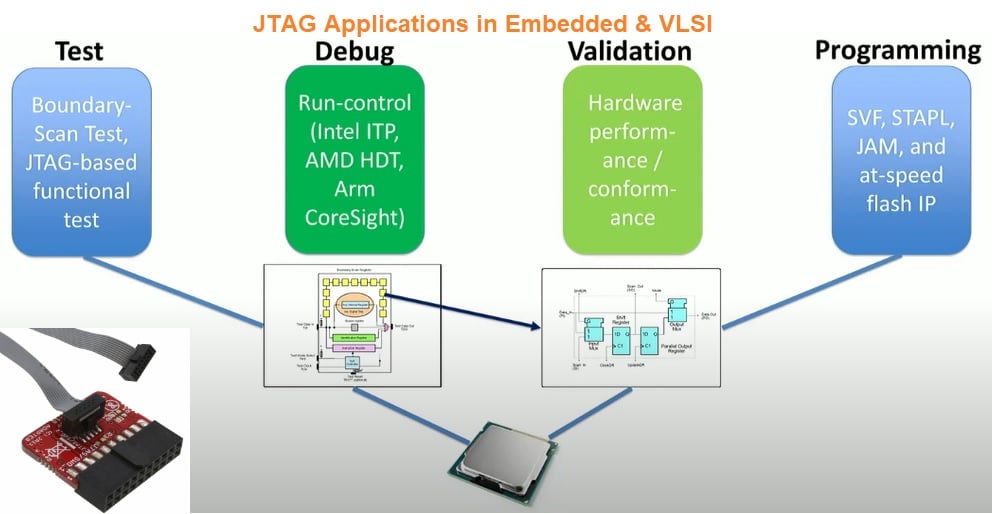

Applications of JTAG Protocol

The JTAG (Joint Test Action Group) protocol has a wide range of applications in the field of electronics and embedded systems. Some of the key applications of the JTAG protocol are as follows:

- Debugging and Testing: One of the primary applications of JTAG is for debugging and testing electronic devices during development and production. JTAG allows engineers to perform boundary-scan testing, enabling them to test the interconnections and integrity of connections between components on a printed circuit board (PCB) without the need for physical access to the board’s individual pins.

- In-System Programming (ISP): JTAG is used for in-system programming of microcontrollers and programmable logic devices. It allows firmware or configuration data to be loaded directly into the device’s memory without the need for a separate programming connector.

- Board-Level Testing: JTAG can be used for board-level testing of complex electronic systems. It enables comprehensive testing of all components on a PCB without requiring physical access to each individual component.

- Boundary-Scan Architecture: The boundary-scan architecture provided by JTAG allows the testing of devices that have JTAG-compliant test access ports. It is particularly useful for testing devices with numerous pins that are otherwise challenging to access.

- Hardware Emulation: JTAG is employed in hardware emulation systems, allowing designers to emulate and test their designs at various stages of development before the physical hardware is available.

- Silicon Debugging: JTAG is used for silicon debugging, enabling engineers to gain insight into the behavior of integrated circuits at the transistor level. This is crucial for diagnosing complex issues and optimizing the design.

- FPGA Configuration: For FPGA (Field-Programmable Gate Array) devices, JTAG is used for configuration and programming. It allows the bitstream (configuration data) to be loaded into the FPGA, defining the logic and interconnections of the hardware circuit.

- Boundary-Scan Testing in System-on-Chip (SoC) Designs: In SoC designs, JTAG is often used for boundary-scan testing of integrated circuits, providing a standardized interface for testing and debugging various components on the chip.

- Security and Anti-Counterfeiting Measures: JTAG can also be used for security purposes, implementing measures to prevent unauthorized access to devices or detecting potential counterfeit components.

Advantages of JTAG Protocol

The Joint Test Action Group (JTAG) protocol, also known as IEEE 1149.1, offers numerous advantages that make it an essential tool in the electronics industry for testing, debugging, and programming integrated circuits (ICs) and printed circuit boards (PCBs). Let’s explore the key advantages of the JTAG protocol:

- Non-Intrusive Testing: JTAG allows for non-intrusive testing, meaning it can test and debug a device without disrupting its normal operation. This is particularly beneficial for complex systems where physical access to individual pins is challenging or impossible.

- Reduced Test Time: JTAG enables parallel testing of multiple pins, resulting in reduced test time. This leads to improved manufacturing throughput and cost-effectiveness.

- Access to Internal Components: The JTAG protocol provides a standardized method to access and control internal components of a device, such as registers and memory. This access is critical for testing and debugging complex digital systems.

- Boundary Scan Testing: JTAG’s boundary scan feature is highly valuable for testing interconnections between different ICs on a PCB. It helps detect and diagnose faults related to open circuits, short circuits, and other connectivity issues.

- In-System Programming (ISP): JTAG facilitates in-system programming of devices, allowing firmware updates and configuration changes without the need for physical access to the IC. This feature simplifies the manufacturing process and enables field updates of devices.

- Debugging Capabilities: JTAG allows engineers to perform extensive hardware debugging. They can set breakpoints, halt the processor’s operation, and examine the processor’s state and memory content. This level of debugging precision helps identify and resolve issues efficiently.

- Hardware Testing and Validation: The standardized nature of JTAG makes it a powerful tool for hardware testing and validation during the development phase. It ensures the reliability and quality of electronic systems.

- Integration with Other Protocols: JTAG can be integrated with other industry protocols and standards, allowing for enhanced capabilities and expanded testing options in specific applications.

- Reverse Engineering: JTAG can be utilized in reverse engineering efforts to extract firmware or other sensitive information from devices. This is valuable for security analysis and understanding proprietary systems.

- Standardized Interface: JTAG’s standardized interface ensures compatibility between devices from different manufacturers, promoting ease of use and interoperability.

Disadvantages of The Joint Test Action Group (JTAG) protocol

While the Joint Test Action Group (JTAG) protocol offers numerous advantages, it also has certain limitations and disadvantages. It’s essential to be aware of these drawbacks when considering the implementation of JTAG in a particular application. Below are some of the disadvantages of the JTAG protocol:

- Pin Requirement: One of the main limitations of JTAG is that it requires additional pins on the device to accommodate the Test Access Port (TAP) interface. In modern ICs where space is at a premium, allocating extra pins for JTAG may not be practical or cost-effective.

- Additional Circuitry: Implementing JTAG in a design requires additional circuitry to support the TAP interface. This can lead to increased complexity and manufacturing costs.

- Test Overhead: While JTAG reduces test time through parallel testing, the overall test time can still be relatively long for complex systems, especially when compared to some specialized, dedicated testing methods.

- Proprietary Implementations: While JTAG is a standardized protocol, some manufacturers may implement proprietary extensions or custom features, which can create compatibility issues between different devices or vendors.

- Speed Limitations: JTAG is designed for low-speed testing and debugging operations. For high-speed testing or applications that require real-time data transfer, JTAG may not be the most suitable option.

- Limited In-System Debugging: While JTAG provides powerful debugging capabilities, it may have limitations when debugging certain real-time applications or deeply embedded systems. In some cases, more advanced debugging tools might be required.

- Potential Security Risks: The same features that make JTAG a powerful tool for testing and debugging, such as in-system programming and boundary scan, can also be potential security risks if not adequately protected. Unauthorized access to the JTAG interface can lead to reverse engineering or unauthorized firmware modifications.

- Impact on Device Performance: In certain applications, enabling JTAG and leaving the TAP connected can impact the overall device performance. This may require careful consideration of when to enable or disable the JTAG interface.

- Development and Training Costs: Integrating JTAG into a design may require additional development effort, and engineers may need specialized training to make the most of its capabilities

Future Development and Enhancement of Joint Test Action Group (JTAG) Protocol

As technology continues to advance, the Joint Test Action Group (JTAG) protocol, also known as IEEE 1149.1, is likely to undergo further developments and enhancements to meet the evolving needs of the electronics industry. Some potential areas of future development and enhancement for JTAG include:

- Higher Speeds: Future advancements may focus on increasing the speed of JTAG communication to accommodate the growing complexity and higher data rates of modern digital systems. Higher speeds would lead to reduced test times and improved efficiency in testing and debugging processes.

- Low-Pin Count JTAG: Efforts may be made to reduce the pin count required for JTAG, making it more suitable for devices with limited available pins. Low-pin counts JTAG solutions could enable testing and debugging on smaller, space-constrained devices.

- Enhanced Security: As cybersecurity concerns continue to grow, JTAG may undergo enhancements to improve its security features. This could include stronger authentication mechanisms, encryption of communication, and measures to prevent unauthorized access to JTAG interfaces.

- Integration with System-on-Chip (SoC): JTAG could be integrated more seamlessly into System-on-Chip (SoC) designs, allowing for enhanced debugging and testing capabilities for complex integrated systems.

- Power Management: Future enhancements may address power management aspects of JTAG to minimize power consumption during testing and debugging operations, making it more suitable for power-sensitive devices.

- Standardization of Debugging Features: Efforts may be made to standardize certain debugging features beyond the core JTAG protocol, allowing for consistent and interoperable debugging across different devices and vendors.

- Support for Advanced Debugging Techniques: Future developments could introduce support for advanced debugging techniques, such as trace-based debugging and real-time analysis of system behavior.

- Integration with Industry Trends: JTAG is likely to integrate with emerging industry trends, such as Internet of Things (IoT) devices, 5G technology, and artificial intelligence. Enhancements may enable JTAG to better cater to the specific testing and debugging needs of these domains.

- Extended Boundary Scan Techniques: Further development of boundary scan testing techniques may improve fault detection capabilities and reduce the impact of faults in complex interconnections.

- Cross-Vendor Collaboration: Continued collaboration between vendors, industry groups, and standardization bodies can lead to more efficient and consistent implementation of JTAG across different devices and applications.

You must be logged in to post a comment.